# A Double-Ended ZVS Half-Bridge Zeta Converter

Ki-Bum Park, Student Member, IEEE, Chong-Eun Kim, Member, IEEE, Gun-Woo Moon, Member, IEEE, and Myung-Joong Youn, Senior Member, IEEE

*Abstract*—A new double-ended type zero-voltage switching (ZVS) half-bridge zeta (HBZ) converter employing a double-ended rectifier (DER) is proposed. The proposed DER for the HBZ converter provides a bidirectional powering path in the rectifier. As a result, the improved voltage waveform of the rectifier reduces the output filter size and voltage stresses on rectifier components. Moreover, it offers a wide ZVS range. In addition, to minimize the secondary snubber loss, a simple lossless snubber is adopted. The operational principles and characteristics of the proposed converter are to be analyzed and verified experimentally.

*Index Terms*—Double ended rectifier (DER), half-bridge zeta (HBZ) converter, single-ended rectifier (SER), zero-voltage switching (ZVS).

#### I. INTRODUCTION

**T** O MINIMIZE the size and weight of pulsewidth modulation (PWM) converters, a high switching frequency is generally required. However, the hard switching of power switch results in high switching loss and high electromagnetic interference (EMI) noise. Therefore, various types of soft switching dc/dc converters have been proposed [1]–[13]. Among them, half-bridge-type converters are very attractive due to the reduced voltage/current stress, reasonable number of components, and zero-voltage switching (ZVS) without auxiliary circuits [6]–[13].

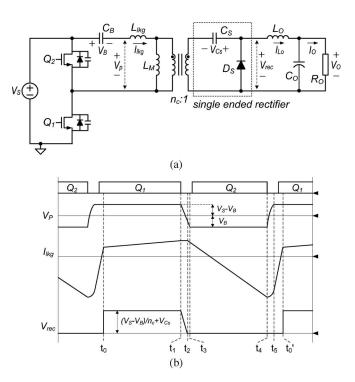

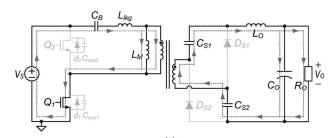

The conventional ZVS half-bridge zeta (HBZ) converter, which is derived from zeta converter, is one of the attractive circuits mentioned before with a wide ZVS range and a linear dc conversion ratio [12]–[16]. However, it features a single-ended-type converter where the power delivery of the rectifier is unidirectional, as shown in Fig. 1. That is, the power is transferred from the primary to the output only in the conducting state of switch  $Q_1$  as can be seen in the voltage waveform of rectifier  $V_{\rm rec}$ .

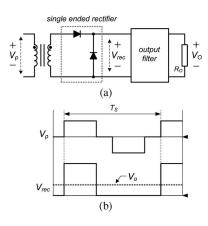

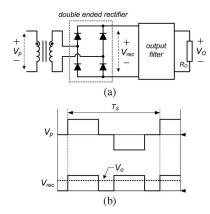

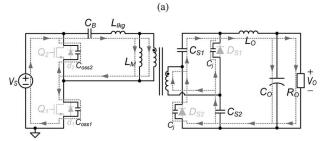

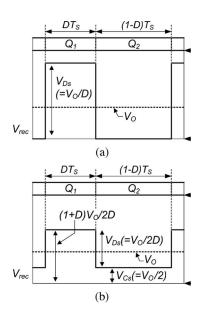

Figs. 2 and 3 show circuit diagrams and voltage waveforms of a usual single-ended rectifier (SER) and a double-ended rectifier (DER), i.e., bridge rectifier, respectively. In general, the

Manuscript received February 27, 2008; revised May 6, 2008. Current version published December 9, 2008. This paper was presented in at the Power Electronics Specialists Conference Orlando, FL. Recommended for publication by Associate Editor F. L. Luo.

K.-B. Park, G.-W. Moon, and M.-J. Youn are with the Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Korea (e-mail: parky@rainbow. kaist.ac.kr; gwmoon@ee.kaist.ac.kr; mmyoun@ee.kaist.ac.kr).

C.-E. Kim was with the Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Korea. He is now with the Power R&D Team, Samsung Electro-Mechanics Company, Suwon-shi 442743, Korea (e-mail: power@angel. kaist.ac.kr).

Color versions of one or more of the figures in this paper are available at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2008.2003189

Fig. 1. Conventional HBZ converter. (a) Circuit diagram. (b) Key waveforms.

unidirectional power delivery of SER needs more transformer secondary turns to achieve the same dc conversion ratio; thus, the higher voltage is impressed on the rectifier devices than the DER where the power delivery of the rectifier is bidirectional. Especially in high-output-voltage applications such as a plasma display panel (PDP) sustaining power module (SPM) where the output voltage is over 170 V, a high voltage stress increases the cost of the device, and degrades its performance [17]–[20]. In addition, a high voltage ringing across the secondary diodes makes this problem more severe, and a large amount of power should be dissipated in the snubber to prevent the additional stress. Moreover, the SER impresses a higher ac voltage on the output filter than the DER, resulting in a larger output filter size [21].

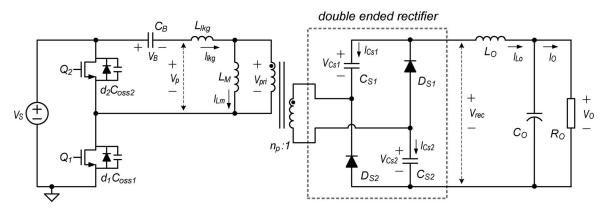

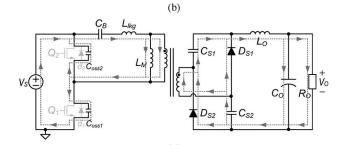

In order to solve aforementioned drawbacks of the conventional single-ended HBZ (SHBZ) converter caused by the SER, this paper proposes the double-ended HBZ (DHBZ) converter employing the DER. As shown in Fig. 4, the structure of proposed DHBZ converter is similar to that of the conventional SHBZ converter except for one additional capacitor and a diode of the rectifier to provide the bidirectional powering path. By adopting the proposed DER, the DHBZ converter reduces the voltage stress on rectifier components and the output filter size while maintaining a wide ZVS range. In addition, to minimize

Fig. 2. SER. (a) Circuit diagram. (b) Voltage waveforms.

Fig. 3. DER. (a) Circuit diagram. (b) Voltage waveforms.

the secondary snubber loss, a simple lossless snubber which does not have any magnetic components is employed.

# **II. OPERATIONAL PRINCIPLE**

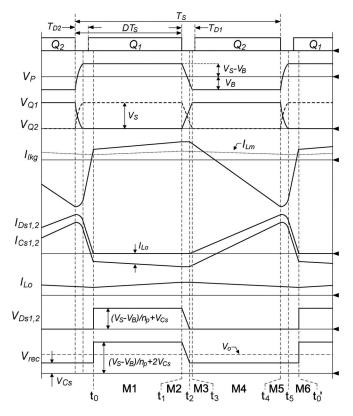

Figs. 5 and 6 show the operational waveforms and topological states of the DHBZ converter, respectively. In order to perform the mode analysis, several assumptions are made as follows: 1) switches are ideal, except for the output capacitor and the internal antiparallel diode; 2) diodes are ideal, except for the junction capacitor; 3) the primary blocking capacitor voltage  $V_B$ , and the secondary capacitor voltage  $V_{Cs1}$ , and  $V_{Cs2}$  are constant. One period is subdivided into six modes and each mode is explained as follows.

*Mode*  $1 [t_0 - t_1]$

$Q_1$  is conducting.  $V_S - V_B$  is applied to the primary side of transformer and  $(V_S - V_B)/n_p + 2V_{Cs}$  is applied to the output filter, where  $V_{Cs} = V_{Cs1} = V_{Cs2}$ . Therefore, as shown in Fig. 6(a), the power is transferred to the output through  $C_{S1}$  and  $C_{S2}$ . The output inductor current  $I_{Lo}(t)$ , magnetizing current  $I_{Lm}(t)$ , and primary current  $I_{lkg}(t)$  are expressed as follows:

$$I_{Lo}(t) = I_{Lo}(t_0) + \frac{(V_S - V_B)/n_p + 2V_{Cs} - V_O}{L_O}(t - t_0) \quad (1)$$

$$I_{Lm}(t) = I_{Lm}(t_0) + \frac{V_S - V_B}{L_M}(t - t_0)$$

<sup>(2)</sup>

$$I_{lkg}(t) = I_{Lm}(t) + \frac{I_{Lo}(t)}{n_p}.$$

(3)

*Mode* 2  $[t_1 - t_2]$

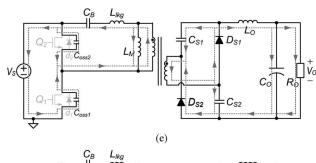

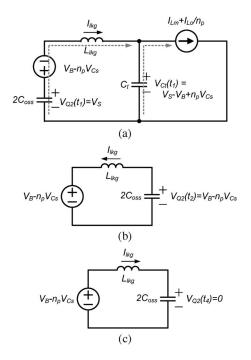

At time  $t_1$ ,  $Q_1$  is turned off. Fig. 7(a) shows the equivalent circuit of this mode, where  $2C_{oss}$ , the total equivalent capacitance of switches, and  $C_t$ , the reflected total equivalent capacitance of diode junction capacitors, are figured out to be  $2C_{oss} = C_{oss1} + C_{oss2}$  and  $C_t = 2C_j/n_p^2$ , respectively.  $I_{Lm}$  and  $I_{Lo}$ , considered as current sources, provide the effect in which  $L_{lkg}$  is small enough that these current sources would discharge  $2C_{oss}$  and  $C_t$  simultaneously. Thus,  $V_{Q2}(t)$ is linearly decreased and the secondary rectifier diode voltage  $V_{D_{s1}}(t)$  and  $V_{D_{s2}}(t)$  are also decreased linearly with a ratio of  $1/n_p$ . If the effect of  $L_{lkg}$  is sufficiently small,  $V_{Q2}(t)$  and  $V_{Ds}(t)[=V_{D_{s1}}(t) = V_{D_{s2}}(t)]$  can be expressed as follows:

$$V_{Q2}(t) = V_S - \frac{I_{Lm}(t_1) + I_{Lo}/n_p}{2C_{\text{oss}} + C_t}(t - t_1)$$

(4)

$$V_{Ds}(t) = \frac{V_{Ct}(t)}{n_p} = \frac{1}{n_p} \left( V_{Q2}(t) - V_B + n_p V_{Cs} \right).$$

(5)

It is noted that  $V_{Q2}(t_1)$ , i.e.,  $V_S$ , is slightly higher than  $V_{Ct}(t_1)$ . Therefore,  $V_{Ct}(t)$  will reach zero little faster than  $V_{Q2}(t)$ . The detailed analysis on the capacitor voltage will be discussed in Section III.

*Mode*  $\Im [t_2 - t_3]$

At time  $t_2$ ,  $D_{S1}$  and  $D_{S2}$  conduct. However,  $V_{Q2}(t)$  is not completely discharged yet. Fig. 7(b) shows the equivalent circuit of this mode. As can be seen in this figure, the energy stored in  $L_{lkg}$  discharges the rest of  $V_{Q2}(t)$ , and  $V_{Q2}(t)$  can be expressed as follows:

$$V_{Q2}(t) = V_{Q2}(t_2) - Z_O I_{lkg}(t_2) \sin(\omega_O(t - t_2))$$

$$Z_O = \sqrt{\frac{L_{lkg}}{2C_{\text{oss}}}}, \qquad \omega_O = \frac{1}{\sqrt{2L_{lkg}C_{\text{oss}}}}.$$

(6)

*Mode*  $4 [t_3 - t_4]$

At time  $t_3$ ,  $V_{Q2}(t)$  reaches zero and the antiparallel diode  $d_2$  conducts. Thus, the ZVS of  $Q_2$  can be achieved. It is noted that the DER provides the powering path from the primary to the output through  $D_{S1}$  and  $D_{S2}$ , as shown in Fig. 6(d). Therefore,  $V_{Cs}$  is applied to the output filter, i.e.,  $V_{rec}(t) = V_{Cs}$ . At the same time,  $C_B$ ,  $C_{S1}$ , and  $C_{S2}$  are resonating with  $L_{lkg}$  since these capacitors are connected magnetically with the transformer. If the resonant period is sufficiently large,  $I_{lkg}$  would be increased linearly, as can be seen in Fig. 5, and reach the high peak current at the end of this mode.  $I_{Lo}(t)$ ,  $I_{Lm}(t)$ , and  $I_{lkg}(t)$  are expressed as follows:

$$I_{Lo}(t) = I_{Lo}(t_3) + \frac{V_O - V_{Cs}}{L_O}(t - t_3)$$

(7)

Fig. 4. Proposed DHBZ converter.

Fig. 5. Key waveforms of the DHBZ converter.

$$I_{Lm}(t) = I_{Lm}(t_3) - \frac{n_p V_{Cs}}{L_M}(t - t_3)$$

(8)

$$I_{lkg}(t) = I_{lkg}(t_3) - \frac{V_B - n_p V_{Cs}}{L_{lkg}}(t - t_3).$$

(9)

*Mode*  $5[t_4 - t_5]$

At time  $t_4$ ,  $Q_2$  is turned off.  $2C_{\text{oss}}$  and  $L_{lkg}$  begin to resonate, as shown in Fig. 7(c). Thus,  $I_{lkg}$  charges  $C_{\text{oss}2}$  and discharges  $C_{\text{oss}1}$ .  $I_{lkg}(t)$  and  $V_{Q2}(t)$  are expressed as follows:

$$I_{lkg}(t) = -\left[ |I_{lkg}(t_4)| \cos(\omega_O(t - t_4)) + \frac{V_B - n_p V_{Cs}}{Z_O} \sin(\omega_O(t - t_4)) \right]$$

(10)

$$V_{Q2}(t) = V_B - n_p V_{Cs} - (V_B - n_p V_{Cs}) \cos(\omega_O(t - t_4)) + Z_O |I_{lkq}(t_4)| \sin(\omega_O(t - t_4)).$$

(11)

*Mode* 6  $[t_5 - t'_0]$

At time  $t_5$ ,  $V_{Q1}(t)$  reaches zero and the antiparallel diode  $d_1$  conducts. Thus, the ZVS of  $Q_1$  can be achieved.  $I_{lkg}$  decreases linearly as in (12) and the voltage across rectifier  $V_{rec}(t)$  maintains  $V_{Cs}$

$$I_{lkg}(t) = I_{lkg}(t_5) + \frac{V_S + V_B - n_p V_{Cs}}{L_{lkg}}(t - t_5).$$

(12)

At time  $t'_0$ , the switching period is completed and the same operation is repeated.

# **III. CHARACTERISTICS**

This section presents the detailed analysis of the DHBZ converter in comparison with the SHBZ converter.

# A. DC Conversion Ratio

To obtain the dc conversion ratio considering the resonant effect between  $C_B$ ,  $C_{S1}$ ,  $C_{S2}$ , and  $L_{lkg}$ , it is assumed that the resonant period is large enough, i.e.,  $V_B$  and  $V_{Cs}$  are constant. The voltage-second balance across  $L_M$  and  $L_O$  can be expressed as in (13) and (14), respectively

$$D(V_S - V_B) = (1 - D)n_p V_{Cs}$$

(13)

$$D\left[2V_{Cs} + \frac{1}{n_p}(V_S - V_B) - V_O\right] = (1 - D)(V_O - V_{Cs}).$$

(14)

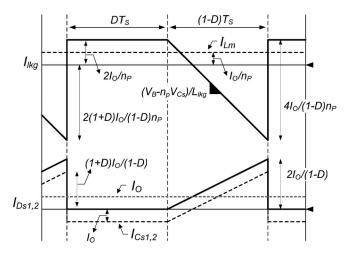

Fig. 8 shows the simplified current waveform of  $I_{lkg}$  regardless of the commutation interval and the following equation is obtained

$$\frac{V_B - n_p V_{Cs}}{L_{lkq}} (1 - D) T_S = \frac{4I_O}{n_p (1 - D)}.$$

(15)

From (13)–(15), the dc conversion ratio can be obtained as

$$\frac{V_O}{V_S} = \frac{2D}{n_p \left[1 + (8DQ)/(n_p^2(1-D)^2)\right]}, \qquad Q = \frac{L_{lkg}}{T_S R_O}.$$

(16)

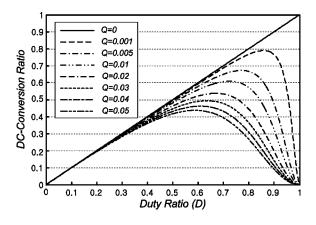

Fig. 9 presents the dc conversion ratio according to the variation of Q, with  $n_p = 2$ . As Q decreases, the dc conversion ratio

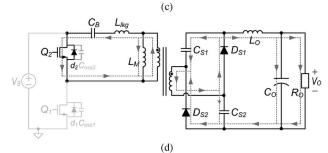

Fig. 6. Topological states of the DHBZ converter. (a) Mode 1  $(t_0 - t_1)$ . (b) Mode 2  $(t_1 - t_2)$ . (c) Mode 3  $(t_2 - t_3)$ . (d) Mode 4  $(t_3 - t_4)$ . (e) Mode 5  $(t_4 - t_5)$ . (f) Mode 6  $(t_5 - t'_0)$ .

Fig. 7. Equivalent circuits. (a)  $t_1 - t_2$ . (b)  $t_2 - t_3$ . (c)  $t_4 - t_5$ .

Fig. 8. Simplified current waveform.

is linearized. If Q is sufficiently small,  $V_B$ ,  $V_{Cs}$ , and  $V_O$  can be approximated as follows:

$$V_B \simeq DV_S \tag{17}$$

$$V_{Cs} \simeq \frac{DV_S}{n_p} \simeq \frac{V_O}{2} \tag{18}$$

$$V_O \simeq \frac{2DV_S}{n_p}.$$

(19)

Compared with the dc conversion ratio of the SHBZ converter, i.e.,  $V_O = DV_S/n_c$ , the DHBZ converter has twice the high dc conversion ratio. Therefore, to operate both converters with the same duty, the turn ratio relationship can be determined as follows:

$$n_p = 2n_c. (20)$$

Fig. 9. DC conversion ratio.

# B. ZVS Condition

As explained in mode 5, ZVS of  $Q_1$  is mainly achieved by the energy stored in  $L_{lkg}$ . From Fig. 7(c), the ZVS condition of  $Q_1$  can be achieved as follows:

$$\frac{1}{2}L_{lkg}I_{lkg}(t_4)^2 > C_{\rm oss}V_S^2 - 2C_{\rm oss}V_S(V_B - n_pV_{Cs}).$$

(21)

Using (18) and (19), the second term on the right-hand side of (21) can be ignored and only the energy terms of  $L_{lkg}$  and  $C_{oss}$  remain. Since the absolute value of  $I_{lkg}(t_4)$  is high, as can be seen in Fig. 5,  $Q_1$  can have a wide ZVS range.

As explained in mode 2, ZVS of  $Q_2$  is mainly achieved by the near current source  $I_{Lm} + I_{Lo}/n_p$  until  $D_{S1}$  and  $D_{S2}$  conduct. Provided that  $2C_{oss} \gg C_t$ , the interval  $t_{12}(=t_2 - t_1)$  can be expressed as follows:

$$t_{12} = \frac{2C_{\rm oss}(V_S - V_B + n_p V_{Cs})}{I_{Lm} + I_{Lo}/n_p}.$$

(22)

After  $D_{S1}$  and  $D_{S2}$  conduct, the rest of ZVS is achieved by the energy stored in  $L_{lkg}$  as explained in mode 3. Thus, the ZVS condition of  $Q_2$  is expressed as follows:

$$\frac{1}{2}L_{lkg}I_{lkg}(t_2)^2 > C_{\rm oss}(V_B - n_p V_{Cs})^2.$$

(23)

Using (18) and (19), (22) can be approximated as in (24) and the right-hand side of (23) can be zero. Therefore, as far as the dead time after  $Q_1$  turn-off, i.e.,  $T_{D1}$ , is longer than  $t_{12}$ , ZVS of  $Q_2$  can always be achieved

$$t_{12} \simeq \frac{2C_{\rm oss}V_S}{I_{Lm} + I_{Lo}/n_p}.$$

(24)

As analyzed before, the ZVS ranges of both switches are wide, specially that of  $Q_2$  is excellent. These ZVS operations are the same as those of the SHBZ converter, which also has a wide ZVS range.

#### C. Device Stress

The current stresses on  $Q_1$  and  $Q_2$  are, from Fig. 8, approximately expressed as in (25) and (26), respectively. In these equations,  $I_{\rm in}$  means the average input current and can be presented as  $2DI_O/n_p$ . The current stresses on secondary diodes

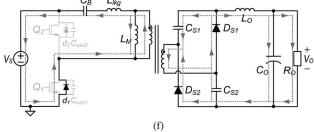

Fig. 10. Rectifier voltage waveforms. (a) SHBZ converter. (b) DHBZ converter.

$D_{S1}$  and  $D_{S2}$  can be expressed as in (27). These are the same as those of the SHBZ converter, since the current shapes of both converters are the same

$$I_{Q1(\max)} = \frac{I_{\rm in}}{D} \tag{25}$$

$$I_{Q2(\max)} = \frac{(1+D)}{D(1-D)} I_{\rm in}$$

(26)

$$I_{D_{S1,2}(\max)} = \frac{2}{1-D} I_O.$$

(27)

The voltage stress on switch is  $V_S$  because of the half-bridge structure. As shown in Fig. 10, the diode voltage stress in the DHBZ converter is expressed as in (28), and is one-half of that of the SHBZ converter, i.e.,  $V_O/D$

$$V_{D_{S1,2}(\max)} = \frac{V_O}{2D}.$$

(28)

$V_{Cs1}$  and  $V_{Cs2}$  are presented in (18), i.e.,  $V_O/2$ , which is also half of that of the SHBZ converter, i.e.,  $V_O$ .

As analyzed before, the DHBZ converter has the reduced voltage stresses on rectifier devices. However, it has high offset in magnetizing current as in (29), increasing the transformer size

$$I_{Lm(\text{avg})} = \frac{I_O}{n_p}.$$

(29)

# D. Output Filter

Fig. 10 shows the comparative waveforms of rectifier voltage  $V_{\rm rec}$  of the SHBZ converter and DHBZ converter. As can be seen in this figure, the ac content of  $V_{\rm rec}$  is much smaller in the DHBZ converter compared with the SHBZ converter. The peak-to-peak filter inductor current ripples of the SHBZ converter and DHBZ converter are obtained as  $(1 - D)V_OT_S/L_O$  and  $(1 - D)V_OT_S/2L_O$ , respectively. Therefore, to achieve the same peak-to-peak filter inductor current ripple, one-half of the filter inductance in the SHBZ converter is used in the DHBZ converter. Consequently, due to the improved waveform of  $V_{\rm rec}$ , the output filter size of the DHBZ converter can be significantly reduced.

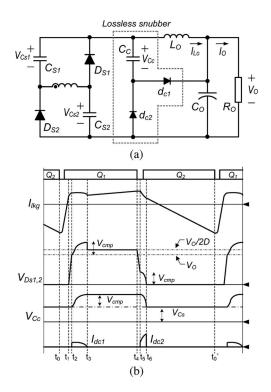

# **IV. LOSSLESS SNUBBER**

In general, isolated converters employing an output inductor suffers from a voltage ringing across the rectifier since the leakage inductance of the transformer and junction capacitance of rectifier diodes are interacted after the rectifier current commutation. This ringing increases the voltage stress on diodes, and thus a snubber is required to prevent the additional voltage stress. The general method is to utilize an resistor-capacitordiode (RCD) snubber across the rectifier; however, the considerable loss degrades the overall efficiency and it becomes more severe in high-output-voltage applications [1], [22], [23]. Therefore, to minimize the snubber loss, the DHBZ converter adopts the simple lossless snubber, as shown in Fig. 11(a) [24]. (The original paper utilizes this circuit for zero-current switching, but it is utilized as a lossless snubber in this paper.) This snubber contains only one capacitor and two diodes without any magnetic components. The basic operation of the DHBZ converter is maintained and the snubber action is related to the transition period. The key waveform of a lossless snubber is shown in Fig. 11(b), and the operational principle is presented as follows.

$V_{Cc}$  is basically charged by  $V_{Cs}$ . After  $Q_2$  is turned off at  $t_0$ , the rectifier current is commutated. At  $t_1$ , the commutation is finished and the junction capacitors of rectifier diodes are charged by the resonance of  $L_{lkg}$ . When  $V_{Ds_{1,2}}$  reaches  $V_O$  at  $t_2$ ,  $d_{c1}$  starts to conduct and  $L_{lkg}$  is resonated with  $C_C$ . Therefore, the ringing is snubbed by the large capacitance  $C_C$ . At  $t_3$ ,  $I_{dc_1}$  reaches zero and  $V_{Cc}$  reaches  $V_{Cs} + V_{cmp}$ . Then,  $V_{Cc}$  keeps the value and  $V_{Ds_{1,2}}$  approaches the steady-state value to  $V_O/2D$ . At  $t_4$ ,  $Q_2$  is turned off and the junction capacitors of diodes are discharged by the filter inductor current as in mode 2 in Section II. At  $t_5$ ,  $d_{c2}$  starts to conduct and both  $C_C$  and junction capacitors of diodes are simultaneously discharged. Due to the large capacitance of  $C_C$ ,  $I_{lkg}$  is little decreased during  $C_C$  discharging operation. At  $t_6$ ,  $D_{S1}$  and  $D_{S2}$  conduct and  $V_{Cc}$  keeps  $V_{Cs}$ .

Although a rather large current flows during the subbing operation, i.e.,  $t_2 - t_3$ , this current directly flows to the output through  $d_{c1}$ . Therefore, it is the powering current, not the circulating current.

Fig. 11. Lossless snubber for the DHBZ converter. (a) Circuit diagram of secondary with the lossless snubber. (b) Key waveforms.

# V. EXPERIMENTAL RESULTS

To verify the performance of the DHBZ converter, a prototype for the high-output-voltage application (42-in PDP SPM) is implemented, where the advantage of the DHBZ converter, i.e., a reduced voltage stress on secondary devices, can be distinctive. The converter has the following specification: input voltage = 385 V, output voltage = 170 V, rated power = 400 W, switching frequency  $F_S = 100$  kHz, switches  $Q_1$  and  $Q_2$ : FQP13N50, secondary diodes  $D_{S1}$  and  $D_{S2}$ : S20LC40, primary and secondary capacitors  $C_B = C_{S1} = C_{S2} = 2.2 \ \mu\text{F}$ , transformer turn ratio  $n_p$ : 29/18, transformer magnetizing inductance  $L_M = 620 \ \mu\text{H}$ , transformer leakage inductance  $L_{lkg} = 25 \ \mu\text{H}$ , output filter inductance  $L_O = 630 \ \mu\text{H}$ , snubber diodes  $d_{c1}$  and  $d_{c2}$ : HER304, and snubber capacitance  $C_C = 10 \ \text{nF}$ .

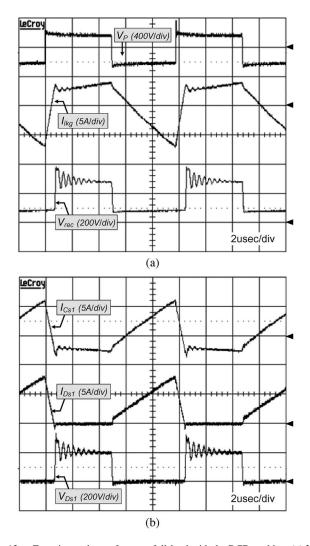

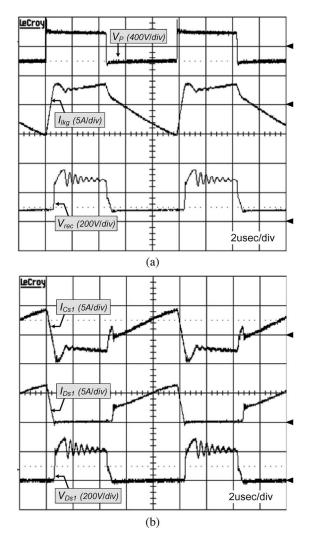

Fig. 12 shows the key experimental waveforms at the fullload condition with an RCD snubber across the rectifier. It is shown that the improved rectifier voltage waveform and other waveforms are agreed well with the theoretical analysis, except for the voltage ringing. The reduced voltage stresses on rectifier components,  $V_{Cs1}(=V_{Cs2})$  and  $V_{Ds1}(=V_{Ds2})$  are also confirmed. To utilize the 400 V rating diodes in the secondary, the voltage stress on diode is limited to 300 V, as shown in Fig. 12(b), using a 15-k $\Omega$  snubber resistance. In case of the SHBZ converter, the voltage stress on diode may exceed 500 V.

Fig. 13 shows the key experimental waveforms at the full-load condition with the lossless snubber mentioned in Section IV. The overall waveforms are similar to that utilizing an RCD snubber except for the snubber action. Using a 10 nF snubber capacitance  $C_C$ , the voltage stress on diode is controlled under

Fig. 12. Experimental waveforms at full-load with the RCD snubber. (a)  $V_P$ ,  $I_{lkg}$ , and  $V_{rec}$ . (b)  $I_{Cs1}$ ,  $I_{DS1}$ , and  $V_{DS1}$ .

300 V, as shown in Fig. 13(b). Because the switching transition is affected by the snubber, some current drop is occurred after  $Q_1$  turn-off. As a result, the peak value of  $I_{lkg}$  at  $Q_2$  turn-off instant is decreased to satisfy the current-second balance of  $C_B$ . This action can decrease the conduction loss in the primary side; however, it gives the detrimental effect on the ZVS operation of  $Q_1$  in return.

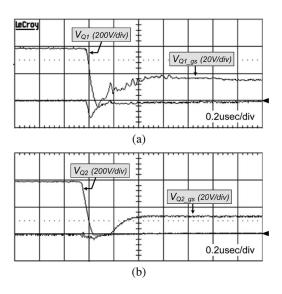

Fig. 14 shows the ZVS waveforms of  $Q_1$  and  $Q_2$ . It is noted that the ZVS of  $Q_1$  is achieved at a 20% load condition by the energy stored in  $L_{lkg}$  from the high peak current, and the ZVS of  $Q_2$  is still achieved at a 10% load condition by the reflected large filter inductor energy.

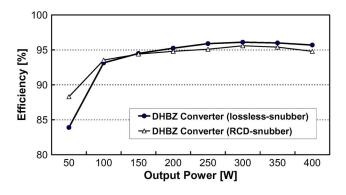

Fig. 15 shows the comparative efficiency curves of the RCD snubber employed case and lossless snubber employed case. With the lossless snubber, the DHBZ converter has higher efficiency over the wide load range. However, the efficiency decreases dramatically with the light load, since the lossless snubber action distorts the converter operation by the large snubbing current compared with the powering current.

Fig. 13. Experimental waveforms at full-load with the lossless snubber. (a)  $V_P$ ,  $I_{lkg}$ , and  $V_{rec}$ . (b)  $I_{Cs1}$ ,  $I_{DS1}$ , and  $V_{DS1}$ .

Fig. 14. ZVS waveforms. (a)  $Q_1$  at 20% load. (b)  $Q_2$  at 10% load.

Fig. 15. Measured efficiency.

# VI. CONCLUSION

A new DHBZ converter, which has a bidirectional powering path in the rectifier, is proposed. The proposed converter has a low voltage stresses on rectifier devices that make it suitable for high-output-voltage applications, and its improved rectifier voltage waveform reduces the output filter size compared with the conventional SHBZ converter. Moreover, it basically has a wide ZVS range due to the characteristic of the HBZ converter. In addition, the lossless snubber is adopted to minimize the secondary snubber loss. Therefore, the DHBZ converter is promised for high-output-voltage applications such as a PDP SPM with high efficiency.

# REFERENCES

- L. H. Mweene, C. A. Wright, and M. F. Schlecht, "A 1 kW 500 kHz front-end converter for a distributed power supply system," *IEEE Trans. Power Electron.*, vol. 6, no. 3, pp. 398–407, Jul. 1991.

- [2] Y. Jang and M. M. Javanovic, "A new PWM ZVS full-bridge converter," IEEE Trans. Power Electron., vol. 22, no. 3, pp. 987–994, May 2007.

- [3] S. S. Lee, S. W. Choi, and G. W. Moon, "High-efficiency active-clamp forward converter with transient current build-up (TCB) ZVS technique," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 310–318, Feb. 2007.

- [4] Y. K. Lo, T. S. Kao, and J. Y. Lin, "Analysis and design of an interleaved active-clamping forward converter," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2323–2332, Aug. 2007.

- [5] Q. Li and P. Wolf, "An analysis of the ZVS two-inductor boost converter under variable frequency operation," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 120–132, Jan. 2007.

- [6] P. Imbertson and N. Mohan, "Asymmetrical duty cycle permits zero switching loss in PWM circuits with no conduction loss penalty," *IEEE Trans. Ind. Appl.*, vol. 29, no. 1, pp. 121–125, Jan. 1993.

- [7] S. Korotkov, V. Meleshin, R. Miftahutdinov, and S. Fraidln, "Softswitched asymmetrical half-bridge DC/DC converter: Steady-state analysis: An analysis of switching processes," in *Proc. TELESCON*, 1997, pp. 177–184.

- [8] T. M. Chen and C. L. Chen, "Analysis and design of asymmetrical half bridge flyback converter," *Proc. Inst. Electr. Eng. Electr. Power Appl.*, vol. 149, no. 6, pp. 433–440, Nov. 2002.

- [9] W. Chen, P. Xu, and F. C. Lee, "The optimization of asymmetric half bridge converter," in *Proc. IEEE APEC*, 2001, pp. 703–707.

- [10] H. S. Choi, "Design consideration of half-bridge LLC resonant converter," J. Power Electron., vol. 7, no. 1, pp. 13–20, Jan. 2007.

- [11] X. Xie, J. Zhang, C. Zhao, Z. Zhao, and Z. Qian, "Analysis and optimization of LLC resonant converter with a novel over-current protection circuit," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 435– 443, Mar. 2007.

- [12] K. Yoshida, T. Isbii, and B. Handa, "A novel zero voltage switching half bridge converter," in *Proc. INTELEC*, 1994, pp. 566–572.

- [13] T. F. Wu, S. A. Liang, and Y. M. Chen, "Design optimization for asymmetrical ZVS-PWM zeta converter," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 39, no. 2, pp. 521–532, Apr. 2003.

- [14] D. C. Matins and G. N. De Abreu, "Application of the ZETA converter in switch-mode power supplies," in *Proc. IEEE APEC*, 1993, pp. 214–220.

- [15] A. Peres, D. C. Martins, and I. Barbi, "ZETA converter applied in power factor correction," in *Proc. IEEE PESC*, 1994, pp. 1152–1157.

- [16] B. Singh, B. P. Singh, and S. Dwivedi, "AD–DC zeta converter for power quality improvement in direct torque controlled PMSM drive," *J. Power Electron.*, vol. 6, no. 2, pp. 146–162, Apr. 2006.

- [17] H. K. Yoon, S. K. Han, J. S. Park, G. W. Moon, and M. J. Youn, "Zero-voltage-switching two-transformer full-bridge PWM converter with loss-less diode-clamp rectifier for PDP sustain power module," *IEEE Trans. Power Electron.*, vol. 21, no. 5, pp. 1243–1252, Sep. 2006.

- [18] W. J. Lee, S. W. Choi, C. E. Kim, and G. W. Moon, "A new PWMcontrolled quasi-resonant converter for high efficiency PDP sustaining power module," in *Proc. IEEE PESC*, 2006, pp. 1–7.

- [19] C. E. Kim, K. B. Park, G. W. Moon, and J. Y. Lee, "New multi-output LLC resonant converter for high efficiency low cost PDP power module," in *Proc. IEEE PESC*, 2006, pp. 1–7.

- [20] S. K. Han, G. W. Moon, and M. J. Youn, "Cost-effective zero-voltage and zero-current switching current-fed energy-recovery display driver for AC plasma display panel," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1081–1088, Jul. 2007.

- [21] Y. S. Lee and B. T. Lin, "Modeling, analysis, and design criteria of actively clamped double-ended converters," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 3, pp. 312–323, Mar. 2000.

- [22] S. Y. Lin and C. L. Chen, "Analysis and design for RCD clamped snubber used in output rectifier of phase shifted full-bridge ZVS converters," *IEEE Trans. Ind. Electron.*, vol. 45, no. 2, pp. 358–359, Apr. 1998.

- [23] K. B. Park, C. E. Kim, G. W. Moon, and M. J. Youn, "Voltage oscillation reduction technique for phase-shift full-bridge converter," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2779–2790, Oct. 2007.

- [24] J. G. Cho, J. W. Baek, C. H. Jeong, and G. H. Rim, "Novel zero-voltage zero-current-switching (ZVZCS) full bridge PWM converter using a simple auxiliary circuit," *IEEE Trans. Ind. Appl.*, vol. 35, no. 1, pp. 15–20, Jan. 1999.

**Ki-Bum Park** (S'07) was born in Korea in 1981. He received the B.S. and M.S. degrees in electrical engineering in 2003 and 2005, respectively, from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, where he is currently working toward the Ph.D. degree.

His current research interests include dc/dc converter, power factor correction (PFC) ac/dc converters, driver circuits of plasma display panel (PDP), backlight inverters of liquid crystal diode (LCD) TV, battery equalizer, and server power system.

**Chong-Eun Kim** (S'04–M'08) received the B.S. degree in electrical engineering from Kyungpook National University, Daegu, Korea, in 2001, and the M.S. and Ph.D. degrees in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2003 and 2008, respectively.

He is currently a Senior Engineering in the Power R&D Team, Samsung Electro-Mechanics Company, Suwon-shi, Korea. His current research interests include dc/dc converters, power factor correction (PFC)

ac/dc converters, plasma display panel (PDP), digital audio amplifiers, and server power system.

**Gun-Woo Moon** (S'92–M'00) received the M.S. and Ph.D. degrees in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1992 and 1996, respectively.

He is currently an Associate Professor in the Department of Electrical Engineering, KAIST. His current research interests include modeling, design and control of power converters, soft-switching power converters, resonant inverters, distributed power systems, power factor correction, electric drive systems,

driver circuits of plasma display panels, and flexible ac transmission systems. Dr. Moon is a member of the Korean Institute of Power Electronics (KIPE),

the Korean Institute of Electrical Engineers (KIEE), the Korea Institute of Telematics and Electronics (KITE), the Korea Institute of Illumination Electronics and Industrial Equipment (KIIEIE), and the Society for Information Display (SID).

**Myung-Joong Youn** (S'74–M'78–SM'98) was born in Seoul, Korea, in 1946. He received the B.S. degree from Seoul National University, Seoul, in 1970, and the M.S. and Ph.D. degrees in electrical engineering from the University of Missouri, Columbia, in 1974 and 1978, respectively.

In 1978, he joined the Air-Craft Equipment Division, General Electric Company, Erie, PA, where he was an Individual Contributor on Aerospace Electrical System Engineering. Since 1983, he has been a Professor at Korea Advanced Institute of Science and

Technology (KAIST), Daejeon, Korea. His current research interests include the areas of power electronics and control, which include the drive systems, rotating electrical machine design, and high-performance switching regulators.

Dr. Youn is a member of the Institution of Electrical Engnieers, U.K., the Korean Institute of Power Electronics (KIPE), the Korean Institute of Electrical Engineers (KIEE), and the Korea Institute of Telematics and Electronics (KITE).