# Dual-Gate MoS<sub>2</sub> FET With a Coplanar-Gate Engineering

Jie Jiang, Ayayi C. Ahyi, and Sarit Dhar

Abstract—A dual-gate multilayer MoS<sub>2</sub> FET with a standard backside gate and a nonstandard coplanar top gate is demonstrated and analyzed. The special feature of this device is that the gate and MoS<sub>2</sub> channel can be directly coupled on the same plane through the bottom-conducting Si substrate. The coplanar-gate MoS<sub>2</sub> FET shows a good performance with a large ON-OFF ratio  $(I_{ON/OFF})$  of  $1.5 \times 10^4$ , a small subthreshold swing (S) of 0.13 V/decade, and a field-effect mobility ( $\mu$ ) of 0.69 cm<sup>2</sup>/Vs, respectively. Furthermore, a large  $V_{\text{th}}$  modulation (-0.55~6.4 V) can be obtained in a dual-gate MoS<sub>2</sub> FET by changing the coplanar-gate bias, which makes the device switch from depletion-mode to enhancement-mode operation, without affecting  $\mu$  and S, regardless of the coplanar-gate bias. In such a dual-gate MoS<sub>2</sub> FET, both top and bottom gates can share the same SiO<sub>2</sub> dielectric, and the deposition of source/drain/gate contact can be combined to a single step. A band diagram with the body effect theory is proposed to explain the device operation mechanism. The coplanar-gate MoS<sub>2</sub> FET with its dual-gate operation and simple fabrication process can provide a good candidate for low-cost 2-D planar nanoelectronics and sensor applications.

*Index Terms*—2-D MoS<sub>2</sub>, coplanar gate, dual gate, FETs, threshold voltage.

# I. INTRODUCTION

**2**-D SEMICONDUCTORS such as  $MoS_2$  have attracted significant interests as layered transition-metal dichalcogenide semiconductors due to their unique electronic, optical, and mechanical properties [1], [2]. 2-D MoS\_2-based FETs show a promising future for many applications, such as photonic detectors [3], ICs [4], and chemical sensors [5]. To explore more functionalities, a dual-gate MoS\_2 FET configuration was proposed as a powerful tool, because the second gate can provide an additional gate control to the MoS\_2 channel [6], [7]. Recently, different groups have demonstrated pioneering works by using dual-gate MoS\_2 FET configurations. For example, Radisavljevic *et al.* [6] reported the metal-insulator transition in MoS\_2 by using a dual-gate device configuration with HfO\_2 top dielectric capping. Tarasov *et al.* [7] optimized the mobility of MoS\_2 by

Manuscript received July 10, 2015; revised September 22, 2015 and October 23, 2015; accepted November 29, 2015. This work was supported by Auburn University. The review of this paper was arranged by Editor H. Shang.

J. Jiang is with the Department of Physics, Auburn University, Auburn, AL 36830 USA, and also with the Institute of Super-Microstructure and Ultrafast Process in Advanced Materials, Hunan Key Laboratory for Super-Microstructure and Ultrafast Process, School of Physics and Electronics, Central South University, Changsha 410083, China (e-mail: jiangjie@csu.edu.cn).

A. C. Ahyi and S. Dhar are with the Department of Physics, Auburn University, Auburn, AL 36830 USA (e-mail: ahyiaya@auburn.edu; szd0024@auburn.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2015.2504582

electrostatic doping in a dual-gate  $MoS_2$  FET with  $Al_2O_3$  top dielectric. More recently, Roy *et al.* [8] successfully fabricated tunnel diodes and transistors by using a dual-gate  $MoS_2$  FET with ZrO<sub>2</sub> top dielectric capping [8]. The dual-gate  $MoS_2$  device structures are usually based on the  $MoS_2$  channel sandwiched between two gate electrodes from which it is electrically isolated by two different gate dielectrics.

From a fabrication perspective, a simpler process with fewer steps is attractive for improving the device yield and reducing the fabrication cost. Recently, an interesting approach was proposed by using side-gate coplanar configuration for GaAs-based high-electron-mobility transistors [9]–[12]. Based on this architecture, the deposition of gate, source, and drain can be completed on the same plane using a one-step process, which greatly simplifies the device processing. This kind of FET has been demonstrated to show promise in highspeed photodetector and logic device applications [9]-[12]. Furthermore, it is to be noted that, in the recent 2-D FET (MoS<sub>2</sub>, graphene) domain, some groups have also reported that the coplanar-gate MoS<sub>2</sub> or graphene FET can be realized by using a top-gate polymer electrolyte or ionic liquid, which connects the gate electrode and 2-D channel in the same plane directly [13]-[16]. Kim et al. [13] demonstrated a coplanargate transparent 2-D graphene transistor for logic circuits on flexible plastic substrate and pressure sensor matrix application [14]. Using this coplanar-gate 2-D FET configuration, Lin et al. [15] recently reported an improved carrier mobility in a coplanar-gate MoS<sub>2</sub> FET by using organic ionic liquid as the top dielectric [15]. Ye et al. [16] successfully demonstrated superconductivity in the multilayer MoS<sub>2</sub> coplanar-gate FET by using top ionic-liquid dielectric [16]. Although these devices show high promise for some important applications, the organic nature of these materials raises concerns about severe device instability under operating conditions.

In this paper, we demonstrate a coplanar-gate multilayer  $MoS_2$  FET without any top dielectric. To the best of our knowledge, for the first time, we find that the  $MoS_2$  channel and a coplanar gate can be directly coupled by the bottom-conducting Si substrate. Based on this configuration, a dual-gate  $MoS_2$  FET is demonstrated by coupling  $MoS_2$  channel and coplanar gate on the same plane directly. The threshold voltage ( $V_{th}$ ) of this device can be tuned from -0.55 to 6.4 V by modulating the coplanar-gate bias from 20 to -15 V. Compared with the traditional dual-gate  $MoS_2$  FET, this device has the following advantages.

- 1) Top gate and bottom gate share the common SiO<sub>2</sub> dielectric.

- 2) The source, drain, and coplanar gate can be deposited in one-step process within the same plane.

0018-9383 © 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

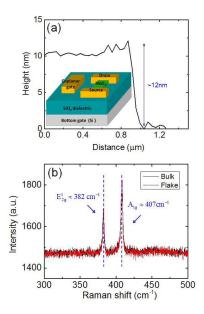

Fig. 1. (a) Height measurement using AFM at the  $MoS_2$  flake edge. Inset: schematic of the coplanar-gate  $MoS_2$  FET. (b) Raman spectra of  $MoS_2$  flake and bulk  $MoS_2$ .

This new gate-engineering method and fabrication approach for  $MoS_2$  FET may provide a new route to realize 2-D planar-integrated nanoelectronics.

# **II. EXPERIMENTAL DETAILS**

MoS<sub>2</sub> flakes were exfoliated from a bulk crystal by mechanical cleavage and subsequently transferred to a highly doped Si substrate with a 290-nm SiO<sub>2</sub> capping layer. The gate, source, and drain electrodes (Ti/Cr/Au: 20/20/130 nm) were patterned by photolithography/liftoff, where the metals were deposited by dc-sputtering. The thickness of MoS<sub>2</sub> flakes was measured by atomic force microscopy (AFM). Raman spectroscopy, employing a Kimmon Electric HeCd laser as the excitation source, was used to evaluate the chemical quality of the flakes. Capacitance–voltage (C-V) characteristics of the devices were measured by Keithley 590 CV analyzer, and current–voltage characteristics were measured by Keithley2400 SMUs in the dark at room temperature.

# **III. RESULTS AND DISCUSSION**

Fig. 1(a) (inset) shows a schematic of the device. The experiment details can be found in the experimental section at the end of the main text. The thickness and chemical nature of exfoliated MoS<sub>2</sub> flakes were measured by AFM and Raman spectroscopy, respectively. Fig. 1(a) shows the profile line information from the AFM measurement for the exfoliated MoS<sub>2</sub> flake with a thickness of ~12 nm. Based on a 0.65-nm thickness per layer value according to [1] and [2], we estimate that the thickness of this MoS<sub>2</sub> flake is ~18 layers. Fig. 1(b) shows the Raman spectra of a sample tested in dark and air ambient environment. In-plane  $E_{2g}^1$  mode (~382 cm<sup>-1</sup>) and out-of-plane  $A_{1g}$  mode (~407 cm<sup>-1</sup>) are observed in both thin MoS<sub>2</sub> flake and bulk MoS<sub>2</sub> flake is very similar to that of the

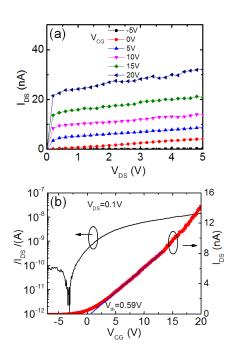

Fig. 2. (a) Output characteristics of coplanar-gate MoS<sub>2</sub> FET. (b) Transfer characteristic of a coplanar-gate MoS<sub>2</sub> FET obtained by sweeping the  $V_{CG}$  from -7 to 20 V with a fixed bias of  $V_{DS} = 0.1$  V.  $V_{CG}$ : coplanar-gate voltage.

bulk MoS<sub>2</sub> flake, indicating good crystalline characteristic and negligible structural modifications in the exfoliated flake [18].

The output and transfer characteristics of coplanar-gate MoS<sub>2</sub> FET can be summarized in Fig. 2(a) and (b), respectively. The output curve is measured by sweeping the values of  $V_{DS}$  from 0 to 5 V with a fixed coplanar-gate  $V_{CG}$  from -5 to 20 V, with 5 V steps. From the output curve, good linear characteristics in the low V<sub>DS</sub> and pinchoff characteristics in the high  $V_{\rm DS}$  regimes were observed, indicating consistence with the traditional FET theory. The transfer curve was obtained by sweeping the coplanar-gate voltage from -7 to 20 V with a fixed  $V_{DS} = 0.1$  V (here, the bottom gate is floating). A large ON-OFF ratio  $(I_{ON/OFF})$ and a small subthreshold swing (S) were found to be  $1.5 \times 10^4$  and 0.13 V/decade, respectively. This is only for a proof-of-concept for a coplanar MoS<sub>2</sub> transistor. To get a stronger coupling between the coplanar gate and the channel, further work needs to be done to improve the device performance, like choosing a large width-to-length ratio (W/L), using a high-k dielectric, etc. A near-zero threshold voltage  $(V_{\rm th} = 0.59 \text{ V})$  was extracted by extrapolating the linear portion of  $I_{DS}-V_{GS}$  curve (as shown in the right linear scale axis) to a zero drain current.

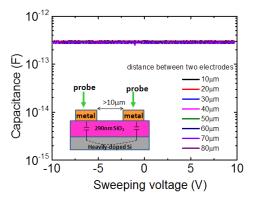

C-V measurements can be used to understand the operation mechanism of a coplanar-gate MoS<sub>2</sub> FET and calculate the field-effect mobility ( $\mu$ ). Using the same silicon wafer with the same oxide, we confirmed that two electrodes deposited on top of the oxide remain capacitively coupled independently of the distance separating them. Fig. 3 shows the C-V measurements (probe frequency: 100 kHz) as a function of coplanar-electrode voltage with different electrode distances (from 10 to 80  $\mu$ m, step = 10  $\mu$ m). A constant value (~0.3 pF) was observed from this figure during sweeping the coplanar-electrode voltage

Fig. 3. C-V measurements as a function of coplanar-electrode voltage with different electrode distances (from 10 to 80  $\mu$ m, step = 10  $\mu$ m).

from -10 to 10 V. In particular, the capacitance values were almost unchanged with the electrode distance increasing from 10 to 80  $\mu$ m. It should be noted that, the previous report has shown that the constant C-V value may be due to screening of the electric field by the highly doped Si layer underneath [19]. The invariance of the capacitance with the change in the electrode distance may indicate that only the capacitance of one of the electrodes and the underlying Si layer matters [19].

Based on the C-V results and the data presented in Fig. 3(b), we calculate the values of  $\mu$  from the linear region of the transfer curve ( $I_{DS}-V_{GS}$ ) according to the equation [20]

$$\mu = \frac{L}{W \times C_{\text{coplanar}} \times V_{\text{DS}}} \times \frac{dI_{\text{DS}}}{dV_G} \tag{1}$$

where  $L = 5 \ \mu m$  is the channel length,  $W = 8 \ \mu m$ is the channel width, and  $C_{coplanar} = 5.85 \ nF/cm^2$  is the SiO<sub>2</sub> dielectric unit capacitance (considering that they are laterally coupled, they are separated by twice the oxide thickness). The field-effect mobility of the device is thus calculated to be 0.69 cm<sup>2</sup>/Vs. It should be noted that this value is underestimated as it does not include the effect of contact resistance between the source/drain metals and MoS<sub>2</sub> and the effect of depletion zone in the Si. Changing the present source/drain metal to Scandium may improve the field-effect mobility of our device as suggested in a recent report [21].

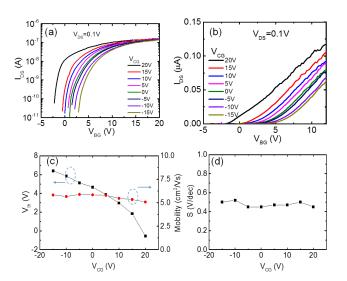

Next, a dual-gate operation of the device with coplanar-gate configuration was characterized. The transfer characteristics in the linear region ( $V_{\rm DS} = 0.1$  V) was measured by sweeping the bottom-conducting Si electrode  $(V_{BG})$  with different coplanargate biases ( $V_{CG}$  from -15 to 20 V, step = 5 V), as shown in Fig. 4(a). From this figure, it is clear that positive coplanargate voltages make the transfer curves shift toward negative gate-voltages, whereas for negative coplanar-gate voltage, the transfer curve shifts in the opposite direction. The  $V_{\rm th}$  value of a dual-gate MoS<sub>2</sub> FET with different coplanar-gate biases was calculated by extrapolating the linear portion of  $I_{DS}-V_{GS}$ curve to a zero drain current, as shown in Fig. 4(b). It was found that the dual-gate  $MoS_2$  FET has a large  $V_{th}$  modulation (-0.55 to 6.4 V) when the coplanar-gate bias is changed from 20 to -15 V, which results in a turnaround from the depletion-mode operation to the enhancement-mode operation.

Fig. 4. (a) Transfer characteristics in the linear region ( $V_{\rm DS} = 0.1$  V), obtained by sweeping the bottom-conducting Si electrode with different values of  $V_{\rm CG}$  (from -15 to 20 V, step = 5 V). (b) Extracted  $V_{\rm th}$  values obtained by extrapolating the linear portion of  $I_{\rm DS}-V_{\rm GS}$  curve to a zero drain current. (c) Extracted values of  $V_{\rm th}$  and  $\mu$  as a function of  $V_{\rm CG}$ . (d) Extracted values of *S* as a function of  $V_{\rm CG}$ .  $V_{\rm CG}$ : coplanar-gate voltage.

Both the depletion mode and the enhancement modes can be used as the basic building blocks to construct complementary 2-D IC, which will have less power consumption and more functionality.

We summarized the extracted values of  $V_{\rm th}$  and  $\mu$  in Fig. 4(c). From this figure,  $V_{\rm th}$  has a nearly linear dependence from -0.55 to 6.4 V as a function of the top coplanargate voltage. Such a dual-gate MoS<sub>2</sub> FET with coplanar gate may have some important applications, such as ionsensitive sensor FETs (ISFETs) [22]. In general, an ideal ISFET should have good sensor characteristics to the variation of external environment (that is through the voltage potential on the additional dielectric). Here, our device shows a great potential for application as an ISFET based on the following reasons: 1)  $V_{\text{th}}$  shows a large variation from -0.55 to 6.4 V as a function of the top coplanar-gate voltage, indicating that good sensor characteristics in the surface potential of a coplanar-gate dielectric region can be observed and 2) Compared with the traditional ISFET, our prototype of the dual-gate MoS<sub>2</sub> FET has less process steps. We do not need to fabricate the additional second gate dielectric, which means the device process can be greatly simplified. Based on the  $V_{\rm th}$  values and (1),  $\mu$  can be extracted from the linear region of transfer curves in Fig. 4(a) by using the SiO<sub>2</sub> dielectric capacitance:  $C_i = (\varepsilon_o \varepsilon_r / d) = 1.19 \times 10^{-8}$  F/cm<sup>2</sup>, where  $\varepsilon_o$  is the dielectric constant of vacuum,  $\varepsilon_r$  is the relative dielectric constant of SiO<sub>2</sub> ( $\varepsilon_r = 3.9$ ), and d is the thickness of the SiO<sub>2</sub> dielectric (d = 290 nm). The results are shown in Fig. 4(c). The  $\mu$  value was calculated to be ~5.4 cm<sup>2</sup>/Vs, which was almost independent of different coplanar-gate voltages. We note that the  $\mu$  value is larger in a dual-gating mode than in a single-gating mode of our device. The possible reason is that it is not true conductivity mobility, but it is the field-effect mobility [23], which increases as charge density increases during dual-gate operation. Compared with the single-gating

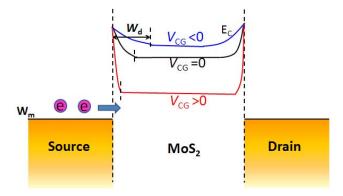

Fig. 5. Schematic energy band diagram of a coplanar dual-gate  $MoS_2$  FET for explaining the  $V_{th}$  shift.

mode, a dual-gating mode can provide stronger electric-field coupling between the gate and the channel (that means a larger ON-current) [24]–[26]. Therefore, larger field-effect mobility can be achieved in a dual-gating mode than a single-gating mode. However, compared with the mobility (several hundreds of cm<sup>2</sup>/Vs) in conventional Si-based MOSFETs, the mobility in our device is still much smaller ( $<10 \text{ cm}^2/\text{Vs}$ ). The mobility of MoS<sub>2</sub> transistors can be grossly underestimated due to very high contact resistances associated with Schottky barriers at the source and drain [21]. This requires better source/drain electrode engineering, In addition, further improvement of the drain current in our coplanar-gate MoS<sub>2</sub> devices could be possible with higher quality  $MoS_2$  thin films and use of high-k gate dielectric to get a stronger gate coupling. Furthermore, the subthreshold swing (S) was found to be  $\sim 0.5$  V/decade with a weak dependence on the different coplanar-gate voltages, as shown in Fig. 4(d), indicating that no additional defects were generated during the continuous coplanar-gate bias [27]. It is also to be noted that, two coplanar-gate electrodes may eliminate any effect due to asymmetry between the coplanar gate and the channel. Unluckily, at present, we have not fabricated the MoS<sub>2</sub> transistor with two coplanar-gate electrodes. In the next work, we shall design two coplanar-gate electrodes into the MoS<sub>2</sub> transistor to examine the effect due to asymmetry in the geometry of the coplanar gate and the channel.

Finally, based on the above results, an energy band diagram similar to the body effect in traditional MOSFET [28] can be proposed to explain the dual-gate modulation in the coplanargate  $MoS_2$  FET as shown in Fig. 5. When the coplanar-gate bias  $(V_{CG})$  is zero, the electrons ejecting from source electrode need to overcome high Schottky barriers at the metal-MoS<sub>2</sub> interface (indicated by the black curve in Fig. 5) [21], [29]. More electrons in the  $MoS_2$  channel will be depleted when a negative  $V_{CG}$  is applied to the top coplanar gate. Therefore, the depletion region at the metal-MoS<sub>2</sub> interface gets larger, which will make the  $V_{\text{th}}$  value of dual-gate MoS<sub>2</sub> FET shift toward positive direction (indicated by the blue curve in Fig. 5). However, when a positive  $V_{CG}$  is applied, the depletion width will be greatly shortened. Thus, the electrons injected from source electrode have a higher probability to tunnel through this shorter depletion width (indicated by red curve in Fig. 5).  $V_{\rm th}$  of the dual-gate MoS<sub>2</sub> FET will shift toward the negative direction accordingly.

### **IV. CONCLUSION**

In summary, we have successfully fabricated the coplanargate multilayer MoS<sub>2</sub> FET without top dielectric. The MoS<sub>2</sub> channel and the coplanar gate are effectively coupled by the bottom-conducting Si substrate. The coplanar-gate MoS<sub>2</sub> FET shows a good performance with a large  $I_{ON/OFF}$  of  $1.5 \times 10^4$ , a small S of 0.13 V/decade, and  $\mu$  of 0.69 cm<sup>2</sup>/Vs, respectively. Furthermore, by employing the back-gate in conjunction with the coplanar gate, a dual-gate MoS<sub>2</sub> FET configuration was realized. Such a dual-gate  $MoS_2$  FET has a large  $V_{th}$ modulation  $(-0.55 \sim 6.4 \text{ V})$  by changing the coplanar-gate bias from 20 to -15 V, which make the device switch from a typical depletion-mode operation to an enhancementmode operation. It was found that the  $\mu$  and S values were  $\sim$ 5.4 cm<sup>2</sup>/Vs and 0.5 V/decade, respectively, regardless of different coplanar-gate biases. The coplanar-gate MoS<sub>2</sub> FET and its dual-gate configuration do not require top dielectric engineering, and the deposition of source/drain/coplanar-gate can be shortened to be a single step. Such a coplanar-gate design with its dual-gate operation with a simple fabrication process may represent a significant step toward low-cost 2-D planar nanoelectronics.

## ACKNOWLEDGMENT

The authors would like to thank Dr. J. Zhong and Prof. W. R. Ashurst for the atomic force microscopy measurement. They would like to thank V. Mirkhani and Prof. M. Park for Raman Spectroscopy. They would also like to thank Y. Zheng and T. Isaacs-Smith for helping with device fabrication.

#### REFERENCES

- Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman, and M. S. Strano, "Electronics and optoelectronics of two-dimensional transition metal dichalcogenides," *Nature Nanotechnol.*, vol. 7, no. 11, pp. 699–712, Nov. 2012.

- [2] S. Z. Butler *et al.*, "Progress, challenges, and opportunities in two-dimensional materials beyond graphene," *ACS Nano*, vol. 7, no. 4, pp. 2898–2926, Apr. 2013.

- [3] O. Lopez-Sanchez, D. Lembke, M. Kayci, A. Radenovic, and A. Kis, "Ultrasensitive photodetectors based on monolayer MoS<sub>2</sub>," *Nature Nanotechnol.*, vol. 8, no. 7, pp. 497–501, Jul. 2013.

- [4] H. Wang *et al.*, "Integrated circuits based on bilayer MoS<sub>2</sub> transistors," *Nano Lett.*, vol. 12, no. 9, pp. 4674–4680, Sep. 2012.

- [5] F. K. Perkins, A. L. Friedman, E. Cobas, P. M. Campbell, G. G. Jernigan, and B. T. Jonker, "Chemical vapor sensing with monolayer MoS<sub>2</sub>," *Nano Lett.*, vol. 13, no. 2, pp. 668–673, Feb. 2013.

- [6] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," *Nature Nanotechnol.*, vol. 6, no. 3, pp. 147–150, Mar. 2011.

- [7] A. Tarasov *et al.*, "Highly uniform trilayer molybdenum disulfide for wafer-scale device fabrication," *Adv. Funct. Mater.*, vol. 24, no. 40, pp. 6389–6400, Oct. 2014.

- [8] T. Roy et al., "Dual-gated MoS<sub>2</sub>/WSe<sub>2</sub> van der Waals tunnel diodes and transistors," ACS Nano, vol. 9, no. 2, pp. 2071–2079, Feb. 2015.

- [9] A. D. Wieck and K. Ploog, "In-plane-gated quantum wire transistor fabricated with directly written focused ion beams," *Appl. Phys. Lett.*, vol. 56, no. 10, pp. 928–930, Mar. 1990.

- [10] Y. Komatsuzaki, K. Saba, K. Onomitsu, H. Yamaguchi, and Y. Horikoshi, "Operating principle and integration of in-plane gate logic devices," *Appl. Phys. Lett.*, vol. 99, no. 24, p. 242106, Dec. 2011.

- [11] T.-H. Chung, W.-H. Lin, Y.-K. Chao, S.-W. Chang, and S.-Y. Lin, "In-plane gate transistors with a 40-μm-wide channel width," *IEEE Electron Device Lett.*, vol. 33, no. 8, pp. 1129–1131, Aug. 2012.

- [12] Y.-A. Liao, W.-H. Lin, Y.-K. Chao, W.-H. Chang, J.-I. Chyi, and S.-Y. Lin, "In-plane gate transistors for photodetector applications," *IEEE Electron Device Lett.*, vol. 34, no. 6, pp. 780–782, Jun. 2013.

- [13] B. J. Kim, S.-K. Lee, M. S. Kang, J.-H. Ahn, and J. H. Cho, "Coplanargate transparent graphene transistors and inverters on plastic," ACS Nano, vol. 6, no. 10, pp. 8646–8651, Sep. 2012.

- [14] Q. Sun *et al.*, "Transparent, low-power pressure sensor matrix based on coplanar-gate graphene transistors," *Adv. Mater.*, vol. 26, no. 27, pp. 4735–4740, Jul. 2014.

- [15] M.-W. Lin *et al.*, "Mobility enhancement and highly efficient gating of monolayer MoS<sub>2</sub> transistors with polymer electrolyte," *J. Phys. D, Appl. Phys.*, vol. 45, no. 34, p. 345102, Aug. 2012.

- [16] J. T. Ye, Y. J. Zhang, R. Akashi, M. S. Bahramy, R. Arita, and Y. Iwasa, "Superconducting dome in a gate-tuned band insulator," *Science*, vol. 338, no. 6111, pp. 1193–1196, Nov. 2012.

- [17] H. Li et al., "From bulk to monolayer MoS<sub>2</sub>: Evolution of Raman scattering," Adv. Funct. Mater., vol. 22, no. 7, pp. 1385–1390, Apr. 2012.

- [18] S. Kim *et al.*, "High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals," *Nature Commun.*, vol. 3, Aug. 2012, Art. ID 1011.

- [19] P. Dianat, R. Prusak, A. Persano, A. Cola, F. Quaranta, and B. Nabet, "An unconventional hybrid variable capacitor with a 2-D electron gas," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 445–451, Feb. 2014.

- [20] Z. Yin *et al.*, "Single-layer MoS<sub>2</sub> phototransistors," ACS Nano, vol. 6, no. 1, pp. 74–80, Jan. 2012.

- [21] S. Das, H.-Y. Chen, A. V. Penumatcha, and J. Appenzeller, "High performance multilayer MoS<sub>2</sub> transistors with scandium contacts," *Nano Lett.*, vol. 13, no. 1, pp. 100–105, Jan. 2012.

- [22] H.-J. Jang and W.-J. Cho, "Performance enhancement of capacitivecoupling dual-gate ion-sensitive field-effect transistor in ultra-thin-body," *Sci. Rep.*, vol. 4, Jun. 2014, Art. ID 5284.

- [23] S. C. Sun and J. D. Plummer, "Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces," *IEEE Trans. Electron Devices*, vol. 27, no. 8, pp. 1497–1508, Aug. 1980.

- [24] N. Rodriguez, S. Cristoloveanu, and F. Gámiz, "Evidence for mobility enhancement in double-gate silicon-on-insulator metal-oxidesemiconductor field-effect transistors," J. Appl. Phys., vol. 102, no. 8, p. 083712, Oct. 2007.

- [25] D. Esseni, M. Mastrapasqua, G. K. Celler, C. Fiegna, L. Selmi, and E. Sangiorgi, "An experimental study of mobility enhancement in ultrathin SOI transistors operated in double-gate mode," *IEEE Trans. Electron Devices*, vol. 50, no. 3, pp. 802–808, Mar. 2003.

- [26] T. Cui and G. Liang, "Dual-gate pentacene organic field-effect transistors based on a nanoassembled SiO<sub>2</sub> nanoparticle thin film as the gate dielectric layer," *Appl. Phys. Lett.*, vol. 86, no. 6, p. 064102, Feb. 2005.

- [27] K. M. Kim *et al.*, "Competitive device performance of low-temperature and all-solution-processed metal-oxide thin-film transistors," *Appl. Phys. Lett.*, vol. 99, no. 24, p. 242109, Dec. 2011.

- [28] J.-P. Colinge and C. A. Colinge, *Physics of Semiconductor Devices*. Kluwer Academic Publishers: Springer, 2002, pp. 192–193.

- [29] X. Tong, E. Ashalley, F. Lin, H. Li, and Z. M. Wang, "Advances in MoS<sub>2</sub>-based field effect transistors (FETs)," *Nano-Micro Lett.*, vol. 7, no. 3, pp. 203–218, Feb. 2015.

**Jie Jiang** received the B.E. and M.E. degrees in electronic science and technology and the Ph.D. degree in physics from Hunan University, Changsha, China, in 2007, 2009, and 2012, respectively.

He was a Post-Doctoral Fellow with Auburn University, Auburn, AL, USA, from 2014 to 2015. He is currently an Assistant Professor with the School of Physics and Electronics, Central South University, Changsha, China.

Ayayi C. Ahyi received the Ph.D. degree in electrical engineering from Université Lille 1, Lille, France, in 1997.

He joined the Physics Department, Auburn University, Auburn, AL, USA, in 2002, where he focused on SiC devices. He has been involved in wide bandgap semiconductors devices, in particular SiC MOS but also GaN devices. He is currently an Associate Research Professor with the Physics Department, Auburn University.

Sarit Dhar received the M.Sc. degree in physics from IIT Kharagpur, Kharagpur, India, in 2000, and the Ph.D. degree in materials science from Vanderbilt University, Nashville, TN, USA, in 2005. He is currently with Auburn University, Auburn, IL, USA. His current research interests include electronic materials and device processing, device physics, dielectric-semiconductor material systems, surface/interface science, and thin-film characterization using ion beams.